There is anecdotal evidence that the PiTubeDirect boot time has degraded recently, such that the Master no longer recognises the Co Pro on power up. This was reported by Mark Haysman in #58.

To try to quantify this, I'm running this program on the Beeb:

10 P%=&2000

20[

30 LDA &FEE0

40 JMP &2000

50]

60 CALL &2000

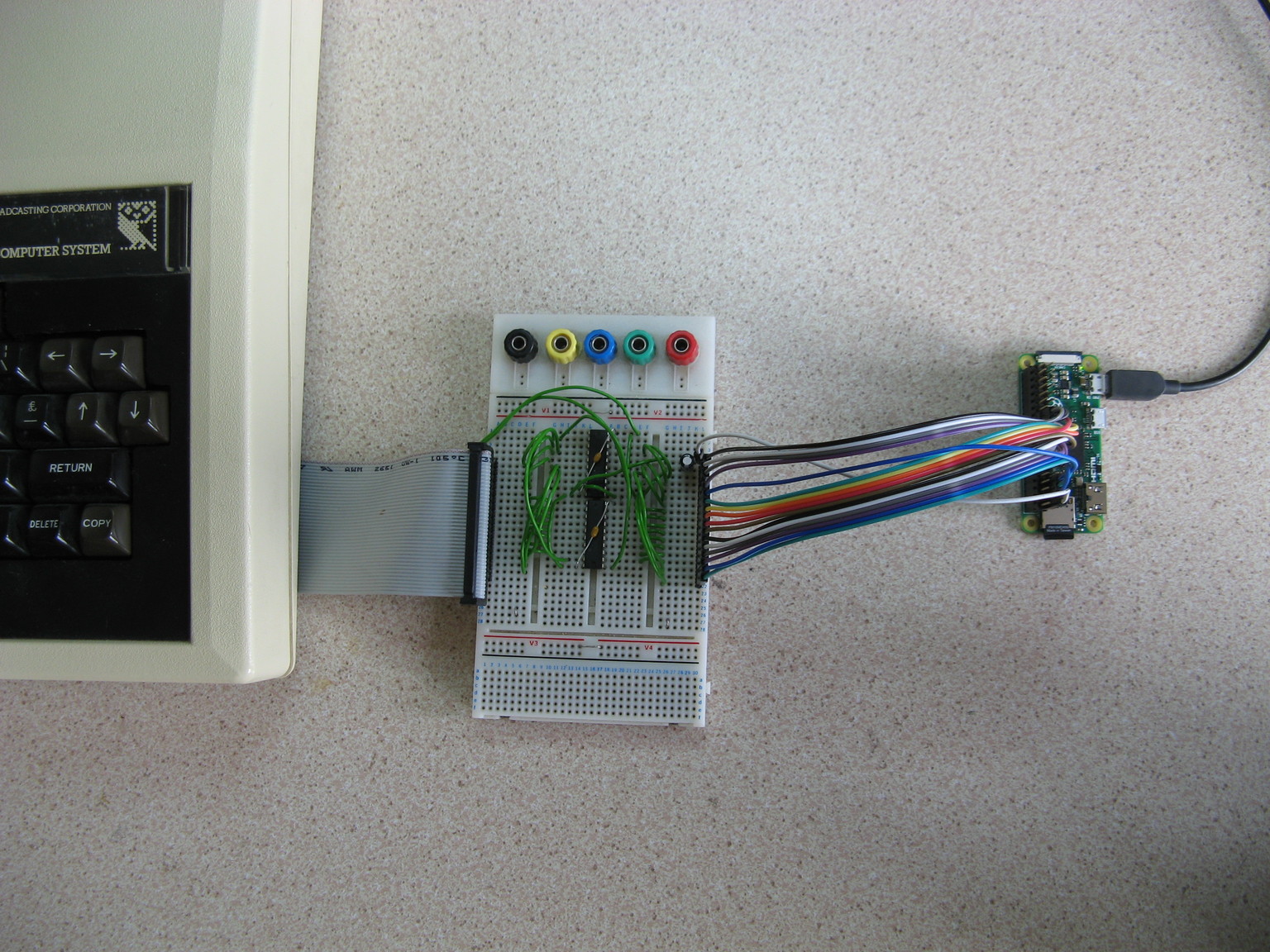

I've got a scope hooked up to the Pi's reset switch, and also to GPIO Pin 24 (D0). This provides a clear indication of how long after reset is released it takes for the Pi to start responding to read requests from the Beeb.

My Master probe's the tube 918ms after power on (measured from VCC reaching 4V). This will probably vary between Masters.

All the SD Cards are freshly formatted with the SD Card Association formatter.

I'll start using my Sandisk Ultra 8GB Class 10 Card and a Pi Zero v1.3:

- 1156/1024ms - Anaconda

- 1160/1023ms - Boa

- 924/798ms - Cobra

- 930/800ms - Diamondback

- 1084/952ms - Egg Eater (rc0)

The first number is the boot time when the SD Card has just been inserted. The second number is the boot time on subsequent reboot cycles.

Note, none of these are recognised on first power up of the Master.

To understand if the SD Card makes a difference, here is the boot time of Diamondback with three different cards:

- 930/800ms - Sandisk Ultra 8GB Class 10 (as above)

- 732/576ms - OV 8GB Class 6

- 812/744ms - Sandisk 4GB Class 4

Out of these cards, the Sandisk Class 10 is not recognised on Boot in my Master, where as the other two are.

Staying with the OV Card, and using the Diamondback release, try different firmware blobs

- 732/576ms - firmware blob released with Diamondback

- 880/726ms - firmware blob released with EggEater

- 882/728ms - current firmware blob, as of 24/7/2018

Staying with the OV Card, and using the EggEater release, try different firmware blobs

- 734/584ms - firmware blob released with Diamondback

- 884/732ms - firmware blob released with EggEater

- 886/732ms - current firmware blob, as of 24/7/2018

So this demonstrates a Firmware Blob change between Diamondback and EggEater has slowed boot down by ~150ms.

Finally, comparing with a Pi Zero and a Pi Zero W:

Pi Zero:

- 732/576ms - original firmware blob released with Diamondback

- 882/728ms - current firmware blob, as of 24/7/2018

Pi Zero W:

- 782/584ms - original firmware blob released with Diamondback

- 1030/787ms - current firmware blob, as of 24/7/2018

Conclusions:

- The firmware blob changes post Diamondback have slowed boot by ~150ms

- The Pi Zero W is slower to boot that the Pi Zero, by 50-150ms (depending on the firmware)

- The sum of (1) and (2) causes my Master to not see the Co Pro on boot

4.The PiTubeDirect kernel has little effect on Boot time between Diamondback and EggEater

Next step is to bisect the firmware blob to see which commit added 150ms.